EP1C6Q240C8N IC FPGA 185 I/O 240QFP

Produkto parametras

apibūdinimas

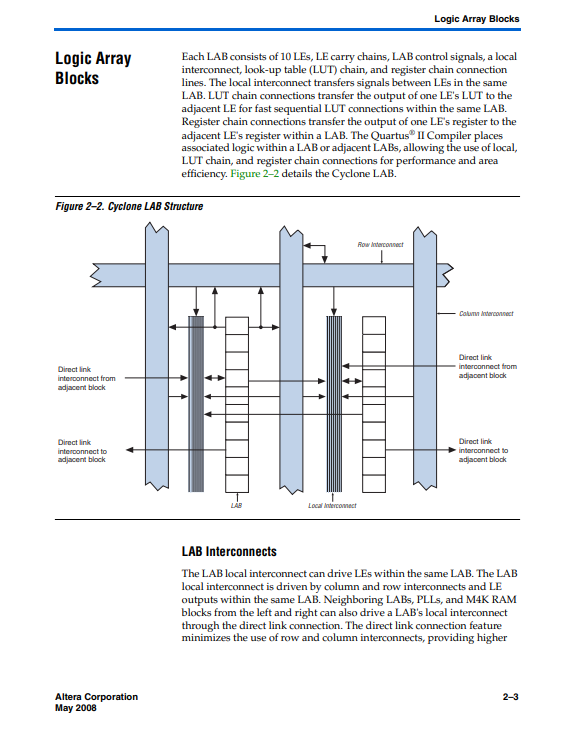

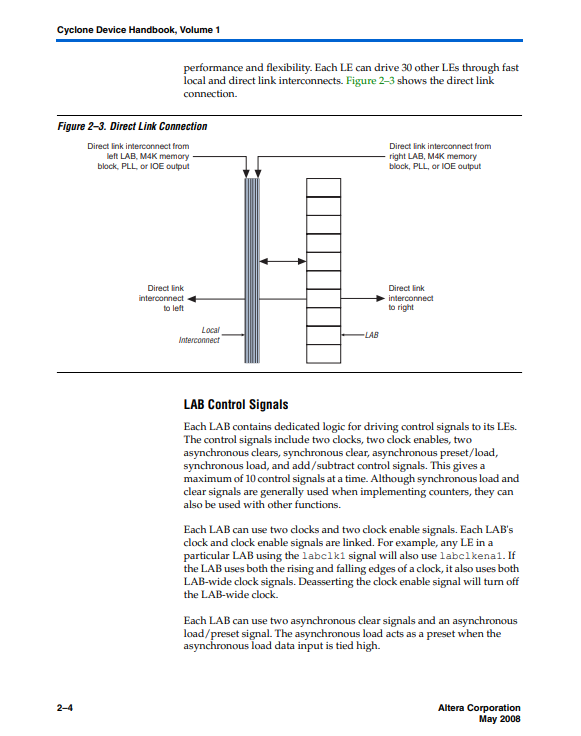

Cyclone® įrenginiuose yra dvimatė eilučių ir stulpelių architektūra, skirta pritaikyti logikai.Skirtingo greičio stulpelių ir eilučių sujungimai užtikrina signalų sujungimus tarp LAB ir įterptųjų atminties blokų.Loginį masyvą sudaro LAB, kurių kiekvienoje LAB yra 10 LE.LE yra mažas logikos vienetas, užtikrinantis efektyvų vartotojo logikos funkcijų įgyvendinimą.LAB yra sugrupuotos į eilutes ir stulpelius visame įrenginyje.Cikloniniai įrenginiai svyruoja nuo 2 910 iki 20 060 LE.M4K RAM blokai yra tikri dviejų prievadų atminties blokai su 4K bitų atmintimi ir paritetu (4 608 bitai).Šie blokai suteikia dedikuotą tikrą dviejų prievadų, paprastą dviejų prievadų arba vieno prievado atmintį iki 36 bitų pločio iki 250 MHz.Šie blokai yra sugrupuoti į stulpelius visame įrenginyje tarp tam tikrų LAB.Cyclone įrenginiai siūlo nuo 60 iki 288 Kbit įterptosios RAM.Kiekvienas „Cyclone“ įrenginio įvesties / išvesties kaištis yra maitinamas įvesties / išvesties elemento (IOE), esančio LAB eilučių ir stulpelių galuose įrenginio periferijoje.Įvesties / išvesties kaiščiai palaiko įvairius vieno galo ir diferencialinius I / O standartus, tokius kaip 66 ir 33 MHz, 64 ir 32 bitų PCI standartas ir LVDS įvesties / išvesties standartas iki 640 Mbps.Kiekviename IOE yra dvikryptis I/O buferis ir trys registrai įvesties, išvesties ir išvesties įgalinimo signalams registruoti.Dvigubos paskirties DQS, DQ ir DM kaiščiai kartu su delsos grandinėmis (naudojamos DDR signalų fazei suderinti) palaiko sąsają su išoriniais atminties įrenginiais, tokiais kaip DDR SDRAM ir FCRAM įrenginiais iki 133 MHz (266 Mbps).Cyclone įrenginiai teikia pasaulinį laikrodžių tinklą ir iki dviejų PLL.Pasaulinį laikrodžių tinklą sudaro aštuonios pasaulinės laikrodžio linijos, kurios veikia visame įrenginyje.Pasaulinis laikrodžių tinklas gali pateikti laikrodžius visiems įrenginio ištekliams, pvz., IOE, LE ir atminties blokams.Visuotinės laikrodžio linijos taip pat gali būti naudojamos valdymo signalams.Cikloniniai PLL suteikia bendrosios paskirties laikrodžio funkciją su laikrodžio dauginimu ir fazių perjungimu, taip pat išorinius išėjimus didelės spartos diferencialiniam įvesties / išvesties palaikymui.

| Specifikacijos: | |

| Atributas | Vertė |

| Kategorija | Integriniai grandynai (IC) |

| Įterptieji – FPGA (lauke programuojamų vartų masyvas) | |

| Mfr | Intel |

| Serija | Ciklonas® |

| Paketas | Padėklas |

| Dalies būsena | Pasenęs |

| LAB/CLB skaičius | 598 |

| Loginių elementų/ląstelių skaičius | 5980 |

| Iš viso RAM bitai | 92160 |

| I/O skaičius | 185 |

| Įtampa – maitinimas | 1,425 V ~ 1,575 V |

| Montavimo tipas | Paviršinis montavimas |

| Darbinė temperatūra | 0°C ~ 85°C (TJ) |

| Pakuotė / Dėklas | 240-BFQFP |

| Tiekėjo įrenginių paketas | 240-PQFP (32x32) |

| Bazinis gaminio numeris | EP1C6 |

SusijęsPRODUKTAI

-

Tel

-

paštas

-

skype

-

WhatsApp

WhatsApp